Designers analyze leakage and dynamic power over a range of abstraction levels as they integrate IP from internal and 3rd party sources. Currently there is no industry standard specification for power model data calculation, so companies develop data translations between proprietary models and combine power results using spreadsheets and custom programs. These are time-consuming to scale and prevent quick system level analysis and optimization. UPTC members participate in and benefit from the co-development of system level power models, utilities, and methodologies in support of the IEEE 2416 UPM standard. Coalition members also consider cross-domain power impacts, such as thermal, and drive the development of these aspects in the standard, thereby supporting integrated power-thermal workflows.

Designers analyze leakage and dynamic power over a range of abstraction levels as they integrate IP from internal and 3rd party sources. Currently there is no industry standard specification for power model data calculation, so companies develop data translations between proprietary models and combine power results using spreadsheets and custom programs. These are time-consuming to scale and prevent quick system level analysis and optimization. UPTC members participate in and benefit from the co-development of system level power models, utilities, and methodologies in support of the IEEE 2416 UPM standard. Coalition members also consider cross-domain power impacts, such as thermal, and drive the development of these aspects in the standard, thereby supporting integrated power-thermal workflows.

As a Coalition member, you can create and analyze power descriptions in custom UPM libraries for your internal design flow by leveraging unlimited access to the end-to-end UPM software suite. In this way, your company can realize savings by enabling methodologies which greatly reduce resources needed to predict and analyze system power budgets.

As a library provider you will see cost savings by simplifying and standardizing your power modeling representations. Using contributors requires fewer characterization runs, greatly reducing compute resources. And as a designer you will see reduced cost through ease of IP integration into power analysis flows.

As an EDA supplier, you have re-distribution rights for solutions co-developed in the UPTC and can provide differentiable value to your customers by innovating on top of those solutions while maintaining compatibility with the UPM standard.

As a design organization, the use of UPM models enable getting to market faster and enables earlier and better power efficiencies by supporting detailed system level power estimation. Automatic power roll-ups are generated with less effort and greater reliability thereby reducing design margins and needless conservatism.

The UPTC provides your company a way to influence other members and present a common voice to the IP and EDA suppliers to implement capabilities and enhancements that are important to your company.

As a member of the UPTC you will maintain backward compatibility with existing design flows, since all UPM innovations are developed while ensuring compatibility with existing standards, including the IEEE 2416 standard and future enhancements to IEEE 1801/UPF for power inten

More efficient IP integration is enabled when utilizing IP delivered with UPM libraries. Having a common standard power modeling language reduces need to translate IP blocks from different sources into proprietary formats. All developers and users “speak the same language.” UPM models are in XML, allowing you to easily add UPM libraries into existing flows through standardized input and output.

Increase accuracy and efficiency is achieved by using the flexible methodologies developed by UPTC to model power, often in a single library, using UPM format to replace calculations represented today in multiple spreadsheets. You can more efficiently analyze the effect of input parameter variations on power, replacing error-prone spreadsheet power calculations.

UPM models are evaluated at analysis run-time with process, voltage, and temperature (PVT) as input parameters, enabling early “what if” power estimation before your set of process corners is finalized for verification

Power consumption of all portions of a design, including IP Blocks, memories, IOs and analog/AMS functions can be automatically rolled-up without requiring inefficient and error prone spreadsheets.

Using a common language for representing power data results in quicker and easier IP Block integration. The flexibility of UPM allows IP Block power models to be built from the top-down using existing equations and tables or from the bottom-up based on standard cell libraries.

As a member you received unlimited use of the UPM software suite with the semantically rich UPM power modeling language, to create interoperable power models using either parameter-based equations or power contributors, or both.

The UPM software suite, developed by Si2, is a growing collection of software components available to UPTC members without any restrictions. The suite currently includes:

As a member of the Coalition, you drive adoption of the IEEE 2416/UPM standard through engaging in UPTC Proof-of-Concept (PoC) projects. Working with other coalition members and Si2 UPM experts, these demonstrations validate the advantages of IEEE 2416/UPM for your company and add requirements to evolve the standard.

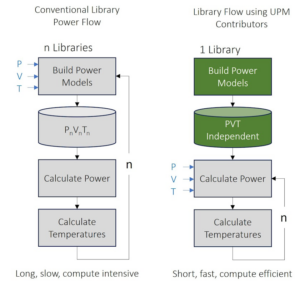

Fewer resources and less time are needed to create UPM libraries because each PVT independent model removes the need for multiple models for each different PVT corner.

Fewer resources and less time are needed to create UPM libraries because each PVT independent model removes the need for multiple models for each different PVT corner.

The contributor (power proxy) extraction, characterization, and UPM library builder allows you to build PVT independence into your library. This enables fast IP and system level model generation at different PVT points.

Using UPM there is no need to re-characterize libraries when a new PVT corner needs to be evaluated.

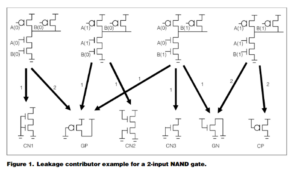

In UPM terminology, power and energy contributors are the various unique power consuming elements in CMOS circuits and act as proxies for actual power. Contributors serve as building blocks for power representation in UPM libraries at gate or higher levels. By supporting PVT variations with the late binding of the PVT values to each contributor, contributors result in significantly smaller libraries compared to the Liberty format. Contributors can be shared across various cells in a library to minimize model generation effort and resources.

An example of leakage contributors for a 2-input NAND gate is shown. When both inputs are at high, leakage is represented with the sum of two GN and two CP contributors. GN and CP contributors are characterized once, but they are repeated numerous times across different cells of a library, thus covering the entire cell library using an optimal number of contributors.

An example of leakage contributors for a 2-input NAND gate is shown. When both inputs are at high, leakage is represented with the sum of two GN and two CP contributors. GN and CP contributors are characterized once, but they are repeated numerous times across different cells of a library, thus covering the entire cell library using an optimal number of contributors.

The UPTC Coalition provides a foundational standard you can use as the base for adding more differentiable value in your products. Redistribution rights enable you to utilize and enhance solutions co-developed by the coalition for use in your products.

Working with other experts you will explore improvements in system level power analysis using auto generated IP block abstract power models and collaborate on efficient power analysis flows using late binding with PVT independent models. You will also explore enhancements to the current power analysis tools and sought-after services for system-power power roll-ups without spreadsheet.

As a Coalition member and EDA tool developer, you will learn about innovations possible with the IEEE 2416/UPM standard directly from the authors. Insights from other coalition members can lead to new product and service opportunities that enhance your production power analysis tools and methodologies.

The UPTC was established to promote industry adoption of the IEEE 2416/UPM power modeling standard. Si2Base Membership and completion of the UPTC Membership Agreement is required. Use of the Si2 UPM Software Suite requires completion of a Beta License Agreement.

The UPTC has one or two chairs from member companies and holds bi-weekly meetings to discuss member Proof-of-Concept projects and enhancements to the UPM implementations.

UPTC members represent their company’s interests in power modeling and are experts in their current power methodology. UPTC member companies can participate in the weekly UPM Working Group which creates demonstrations for new features of the standard.

The UPM working group provides education, outreach and publicity for the IEEE 2416/UPM standard. The Chair leads weekly technical meetings to develop use cases, conference presentations, journal articles, and blog posts to demonstrate new features of the standard. The UPM working group is open to all UPTC members.

UPTC members lead Proof-of-Concept projects to promote adoption of IEEE 2416/UPM in their power analysis flow. Current updates on Proof-of-Concept projects are given at each UPTC meeting.

UPTC members are the advocates for IEEE 2416/UPM in their companies, promoting it’s application in different business units. End user company members advocate for support of IEEE 2416/UPM with their EDA power tool suppliers.

EDA Supplier members advocate for internal solutions to provide IEEE 2416/UPM libraries for system-level IP. Suppliers can innovate on the standard to develop new system-level modeling capabilities to benefit their companies and industry.

System-Level Power Analysis with Unified Power Models

Learn how to develop IEEE 2416/UPM power data models, configure them to interoperate with UPF/1801 power state models, and use them with emerging system-level power analysis tools.

System-Level Industry Experience with Unified Power Models

Learn about semiconductor industry experience with IEEE 2416/UPM and how to use for Mixed signal analysis

2416-2019 – IEEE Standard for Power Modeling to Enable System-Level Analysis